#### **EXPERIMENT TITLE 1.2**

| Stude        | ent Name:                                 | UID:                    |                |

|--------------|-------------------------------------------|-------------------------|----------------|

| Branc        | ch: CSE                                   |                         | Section/Group: |

| Seme         | ster: 2                                   |                         |                |

| Subje        | ct Name: BASIC ELECTRICAL AN              | ID ELECTRONICS ENGIN    | EERING         |

|              |                                           |                         |                |

| <u>Aim:</u>  |                                           |                         |                |

| To veri      | fy Kirchhoff's Voltage Law (KVL) and stud | ly its limitations.     |                |

|              |                                           |                         |                |

| <u>Appar</u> | atus:                                     |                         |                |

| S.NO.        | EQUIPMENT NAME                            | SPECIFICATIONS & RATING | QUANTITY       |

| 1            | Regular variable DC Supply                | 0-30 V , 0-2 A          | 1              |

| 2            | Digital Multimeter                        | 0-30 V                  | 6              |

| 2            | Pocietors                                 | Of Different Values     | 6              |

As Per Requirement

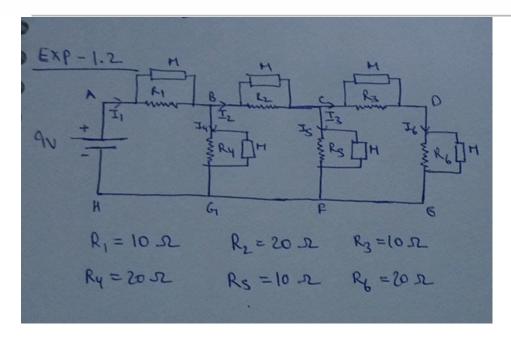

# +Circuit Diagram:

**Connecting Wires**

4

#### **Steps for experiment:**

- 1. The circuit is connected as shown in Circuit Diagram above.

- 2. The voltage of the DC supply was set at 9 V.

- 3. Different values of R1 to R6 were taken and readings of I1 to I6 were noted down.

- 4. Accordingly, only one set of readings was taken at 9 V DC supply.

- 5. The observations were recorded in Table.

### Calculations/Theorems /Formulas used etc

Applying KVL in loop ABGH, V = I1.R1 + I4.R4 or V = V1 + V4

Applying KVL in loop BCFG, V4= I2.R2 + I5.R5 or V4= V2+ V5

Applying KVL in loop CDEF, V5= I3.R3 + I.6.R6 or V5 = V3 + V6

#### **Observations/Discussions:**

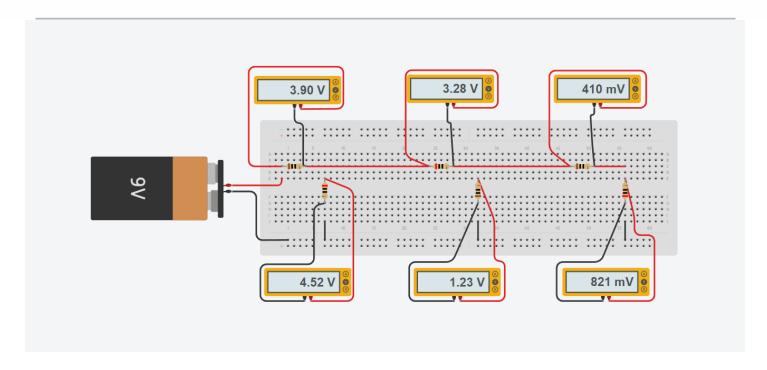

**CIRCUIT SIMULATION**

| S.NO. | SUPPLY VOLTAGE | VOLTMETER 1 | VOLTMETER 2 | VOLTMETER | VOLTMETER | VOLTMETER | VOLTMETER |

|-------|----------------|-------------|-------------|-----------|-----------|-----------|-----------|

|       | (V)            | (V1)        | (V2)        | 3 (V3)    | 4 (V4)    | 5 (V5)    | 6 (V6)    |

| 1     | 9 V            | 3.90 V      | 3.28 V      | 410 mV    | 4.52 V    | 1.23 V    | 821 mV    |

## **Result/Output/Writing Summary:**

As per Kirchhoff's Voltage Law, the theoretical and calculated values of algebraic sum of emfs and voltage drops.

| S.NO. | CALCULATED VALUE OF VOLTAGE (V) |             | THEORITICAL VALUE OF VOLTAGE |          |         | PERCENTAGE ERROR |          |         |           |

|-------|---------------------------------|-------------|------------------------------|----------|---------|------------------|----------|---------|-----------|

|       |                                 |             |                              | (V)      |         |                  |          |         |           |

|       | V = V1 +                        | V4= V2+ V5  | V5 = V3 +                    | V = V1 + | V4= V2+ | V5 = V3 +        | V = V1 + | V4= V2+ | V5 = V3 + |

|       | V4                              |             | V6                           | V4       | V5      | V6               | V4       | V5      | V6        |

| 1.    | 3.90 +                          | 3.28 + 1.23 | 0.41 + 0.82                  | 9 V      | 4.52 V  | 1.23 V           | 0.64 %   | 0.22 %  | NO        |

|       | 4.52 =                          | = 4.51 V    | = 1.23 V                     |          |         |                  |          |         | ERROR     |

|       | 8.42 V                          |             |                              |          |         |                  |          |         |           |

## Graphs (If Any): Image /Soft copy of graph paper to be attached here

**NO GRAPH**

#### **Sources Of Error:**

- 1. Internal resistance of DC battery.

- 2. Internal resistance of multimeter viz. voltmeter and ammeter.

- 3. Internal resistance of connecting wires.

- 4. Heating effect of rheostat coil (Joule's law of electric heating)

- 5. All the sources of error related to multimeter.

### **Learning outcomes (What I have learnt):**

- 1. Application of KVL.

- 2. Not applicable to circuits having distributed elements.

#### **Evaluation Grid:**

| Sr. No. | Parameters                                                                                                   | Marks Obtained        | Maximum Marks |

|---------|--------------------------------------------------------------------------------------------------------------|-----------------------|---------------|

| 1.      | Worksheet completion including writing learning objectives/Outcomes.(To be submitted at the end of the day). |                       | 10            |

| 2.      | Post Lab Quiz Result.                                                                                        |                       | 5             |

| 3.      | Student Engagement in Simulation/Demonstration/Performance and Controls/Pre-Lab Questions.                   |                       | 5             |

|         | Signature of Faculty (with Date):                                                                            | Total Marks Obtained: |               |